Flash

1.Flash 簡介

1.1 簡介

- 記憶體RAM?ROM?

- RAM: 隨機存取記憶體(Random Access Memory)

- 屬於volatile memory(揮發性記憶體),需要保持通電才能儲存資料

- 內部資料可以任意讀寫,用來存放由硬碟載入的程式或資料供CPU處理運算

- EX:main memory

- 分成DRAM、SRAM

- DRAM(Dynamic Random Access Memory):所儲存的數據需要週期性地更新

- SRAM(Static Random Access Memory):只要保持通電,裡面儲存的資料就可以恆常保持

- ROM: 唯讀記憶體(Read Only Memory)

- 屬於非揮發性記憶體(non-volatile memory,縮寫NVRAM),不須保持通電就能儲存資料

- 但資料一但寫入就無法修改,除非透過特殊的方式(例如EPROM用紫外光照射)才能達成

- 適合放重要且不能被刪除的資料

- ROM 嚴格來講是指在製造時就將資料固定了。廣義上是指一般時候只讀,但仍可用某種方式改寫,細分為PROM (Programmable Read-Only Memory,只能寫一次)、EPROM (Erasable Programmable Read-Only Memory,可用紫外線抹除再寫)、EEPROM (Electrically-Erasable Programmable Read-Only Memory,電子式抹除再寫)

- EX:BIOS早期放在ROM中,但隨著BIOS大小和複雜程度增加,硬體更新的速度快,以至於BIOS也必須更新以支援新硬體,於是BIOS就改成存在EEPROM或快閃記憶體中讓使用者可以更新

- EPROM: 可抹除可編程唯讀記憶體(Erasable Programmable Read Only

Memory,EPROM)

- 利用高電壓將資料編程寫入,但抹除時需將線路曝光於紫外線下一段時間,資料始可被清空。

- 封裝外殼上會留一個石英玻璃所製的透明窗以便進行紫外線曝光。

- 寫入程式後通常會用貼紙遮蓋透明窗,以防日久不慎曝光過量影響資料。

- EEPROM: 電子抹除式可複寫唯讀記憶體(Electrically-Erasable

Programmable Read-Only Memory)

- 是一種可以通過電子方式多次複寫的半導體存儲設備。相比EPROM,EEPROM不需要用紫外線照射,也不需取下,就可以用特定的電壓,來抹除晶片上的訊息,以便寫入新的資料。

- EEPROM有兩種種類:序列式(serial)、並列式(parallel),其中並列式通常會以Flash來稱呼。

- 除電源線外,串列式通訊口只使用1~4隻接線來傳遞訊號,所需接腳較並列式少

- 1線:1-Wire(型號以93為開頭) 、UNI/O(型號以11為開頭)

- 2線:I2C(型號以24為開頭)

- 3線:Microwire(型號以93為開頭) 、SPI(型號以25為開頭)

- 資料更新方式:以位元組為單位

- Flash Memory:

- 於1984年發表,Intel之後於1988年發表第一款商業型的NOR Flash晶片

- 以價格便宜、位元密度接手EEPROM的市場位置

- 主要用於一般性資料儲存,以及在電腦及其他數位產品間交換傳輸資料

- EX:記憶卡、隨身碟的儲存媒介

- 快閃記憶體是一種特殊的、以大區塊(blocks)抹寫的EEPROM,寫入大小取決於記憶體控制器本身,介於256KB~20MB不等

- EEPROM只允許單執行緒重寫資料,但快閃記憶體卻可支援多執行緒同時在多個地方寫資料

- 目前主機板的BIOS幾乎都是透過Flash memory儲存

- RAM: 隨機存取記憶體(Random Access Memory)

1.2 Flash原理介紹

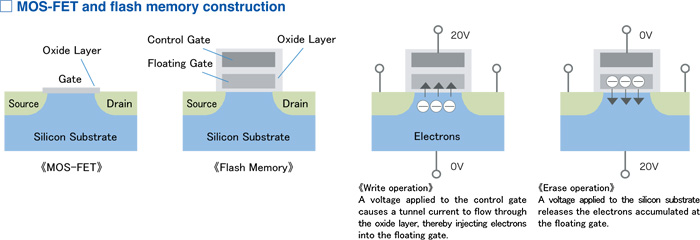

當給予電晶體(MOSFET)的Gate端正電壓後,通道會呈現導通狀態,意即電流會從Source端流到Drain端

Flash的基本架構則是在原本電晶體的Gate端上加入一層特殊氧化層,使得電子可以在沒電壓供應的情況下,持續儲存在Floating Gate

清除(Erase)的方式是在Control Gate給予大約-9~-12V的電壓,並且Source給予大約6V的電壓,清除後的Cell的狀態為bit 1

寫入(Write) bit 0的方式是在Control Gate給予大約12V的電壓,並且Drain給予大約7V的電壓

讀取(Read)的方式是在Control Gate給予大約5V的電壓,如此一來通道會依據Floating Gate的狀態,出現電流,之後再依據電流大小來判斷是1還是0

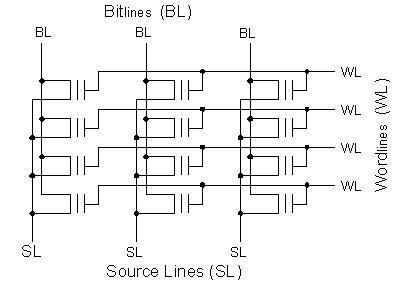

Bit Line: Drain

Word Line: Gate

Source Line: Source

1.3 NOR/NAND Flash介紹

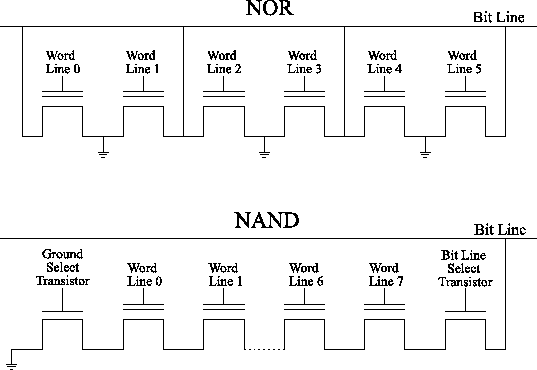

- NOR Flash

- Intel於1988年發表

- 支援隨機存取,讀資料的方式跟RAM接近,給address,data就能讀出

- NOR的特點是原地執行(XIP, eXecute In Place),這樣應用程序可以直接在flash memory內運行,不必再把資料讀到系統RAM中

- 每次寫入/擦除都是以1 block為單位;1 block = 16~128 KBytes

- 小容量(1~4MB)時具有很高的成本效益,但是很低的寫入和擦除速度大大影響了它的性能

- NOR flash佔據了容量為1~16MB閃存市場的大部分,因隨機存取快,應用在手機中

- NOR的擦寫週期壽命是一萬~十萬次

- 適合用於儲存不需經常更新的程式,例如BIOS或韌體

- NAND Flash

- Toshiba於1989年發表

- 適用於大容量,更低的寫入和擦除時間,高密度(單元尺寸是NOR Flash的一半),高壽命(10倍左右),低製造成本

- I/O pin只有8個,只允許連續讀取,所以不適合用於電腦主記憶體(不支援隨機存取)

- 讀寫操作以1 page為單位,擦除(Erase)以1 block為單位

- 1 block = 32 pages;每個block的單位依照廠商製造的不同有區別,介於8~32 KBytes之間

- NAND擦除單元更小,因此擦除速度(4ms)比NOR的(5s)快

- 適合於資料儲存,例如:MMC、固態硬碟(SSD)、USB 3.0隨身碟、手機、數位相機

- 甚至手機、MP3撥放器用NAND Flash當作存放多媒體檔案的媒介,原因在於成本、空間、還有寫入資料的速度

- NAND閃存中每個區塊的最大擦寫次數是一百萬次

1.4 NOR/NAND比較

| ============= NOR Flash | 讀取速度快 |

寫入速度慢 |

擦除速度慢 |

容量小 |

成本高 |

市佔率 | ================+ 減少 | |

| NAND Flash | 中 | 快 | 快 | 大 | 低 |

- 關於NAND Flash 與 NOR Flash的比較可參考 http://www.8051faq.com.cn/manager/download/20077633203664115781250.PDF

2.Flash 記憶體架構介紹

2.1 In memory architecture

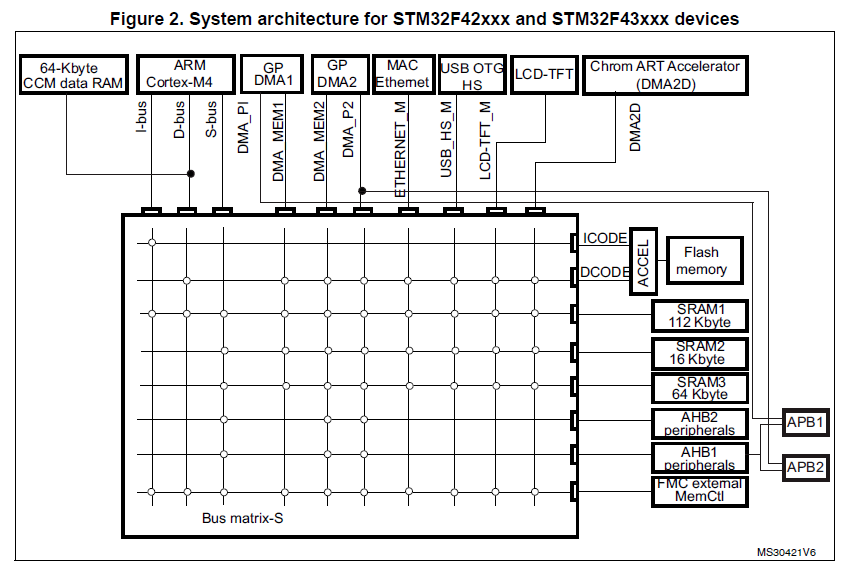

Bus Matrix:(利用round-robin演算法來仲裁) 上方為master,右方為slave,bus matrix提供master可concurrent並有效率進行存取slave。

DM00031020-referenceManual P.62

DM00031020-referenceManual P.62

- AHB(Advanced High-performance Bus): AMBA的一部分,負責連接高性能高頻寬的模組,例如processor, DMA controller, memory

- APB(Advanced Peripheral Bus): AMBA的一部分,負責連接低頻寬的周邊,例如UART

- AMBA(Advanced Microcontroller Bus Architecture): ARM架構下系統晶片(SoC)設計中的一種匯流排架構

- DMA(Direct Memory Access): 允許介面裝置與記憶體之間直接轉移資料,而不需經由CPU的參與

- FMC(Flexible memory controller): 用來連接擴充記憶裝置的控制器,比起FSMC(Flexible Static memory controller),增加了The Synchronous DRAM (SDRAM) controller ,允許存許DRAM,以及SRAM, Flash, PSRAM, SDRAM等記憶體。

- Internal SRAM總容量 = 256KB = 64KB CCM data RAM + SRAM 112KB + SRAM 16KB + SRAM 64KB。

- I-Bus(Instruction Bus): 用來傳遞指令

- D-Bus(Data Bus): 用來傳遞資料

- S-Bus(System Bus): 用來傳遞周邊或是SRAM的系統資料

- SRAM連接至I-bus,可用來加快程式的速度;並且連接至D-bus,加快存取data的速度。

- CCM(Core Coupled Memory):是給CPU專用的64KB RAM,不會經過上圖的Bus Matrix,而是透過D-Bus直接與CPU相連,當SRAM被其他硬體使用時,CPU可以使用CCM以達到零等待。記憶體位址在 0x1000 0000 - 0x1000FFFF,與一般的SRAM不連續,而且DMA和周邊也無法直接使用他們,所以一般user的程式完全無法感覺有這64KB的CCM,可用於stack, heap, global variables, critical OS data或做高速運算緩衝(例如JPEG编解碼等);此外也可以直接拿來當做額外的記憶體使用。

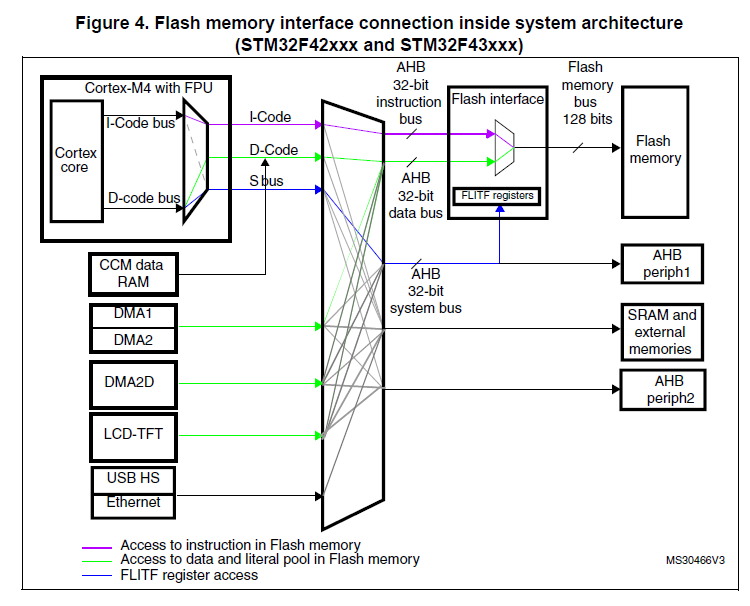

- Flash memory: CPU透過AHB I-Code及D-Code來存取Flash,另外可透過ACCEL加速程式執行。

- ACCEL : Adaptive real-time memory accelerator (ART

Accelerator),可以執行Instruction Prefetch, Instruction cache

memory和Data management來加速執行指令的速度。

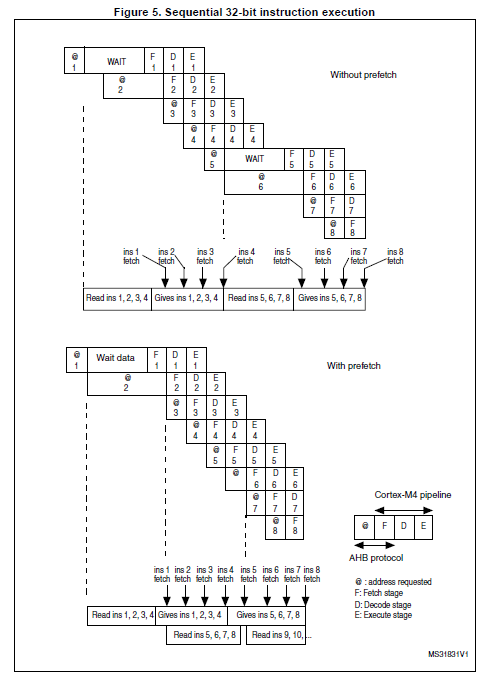

- Instruction Prefetch:

因為Flash的存取速度比起Cortex-M4(180MHz)要慢取多,因此需要一塊記憶體來做Instruction

Prefetch來達到0 Wait Sate,每個flash

memory的讀取動作可以讀取128-bits的指令(4個32bits指令或8個16bits指令),所以在循序讀取code的時候,至少需要四個CPU

cycles來執行上一串指令。而Instruction

Prefetch可以事先讀取下一串指令,不需要Wait State。設定FLASH_ACR

register裡的PRFTEN bit可以開啟Prefetch功能。

- Instruction cache memory: 為了減少Jump指令的執行時間,有必有保留一塊64條128-bit的Cache Memory,只要開啟FLASH_ACR register的ICEN bit就可以開啟這個功能。每次要求的資料假使不在Cache裡,就會將它放進Cache,若有,CPU就可以直接從Cache讀取,避免延遲的時間。當Cache滿時,則根據LRU(least recently used)原則,將最近最少用的資料清掉。

- Data management: 在CPU Pipeline執行階段時,需要從定字池(Literal pools)透過D-Bus取得定字(Literal),而這個動作會使CPU暫時陷入停頓的狀態,為了減少浪費的時間,必須將存取D-code的優先權調高過I-code的,如果有些特定定字池是很常用的,可以透過設定FLASH_ACR register的DCEN bit,這個功能有些類似instruction cache memory,但它的大小只有8條128-bit。(LDR r0, =0 的 =0就是一個literal,編譯器會在記憶體放一個0,放0的位址則會用一個literal來代表,因此當取得這個literal時需要到literal pool找尋它代表的位址)

- Instruction Prefetch:

因為Flash的存取速度比起Cortex-M4(180MHz)要慢取多,因此需要一塊記憶體來做Instruction

Prefetch來達到0 Wait Sate,每個flash

memory的讀取動作可以讀取128-bits的指令(4個32bits指令或8個16bits指令),所以在循序讀取code的時候,至少需要四個CPU

cycles來執行上一串指令。而Instruction

Prefetch可以事先讀取下一串指令,不需要Wait State。設定FLASH_ACR

register裡的PRFTEN bit可以開啟Prefetch功能。

2.2 Flash interface in system architecture

DM00031020-referenceManual P.74

DM00031020-referenceManual P.74

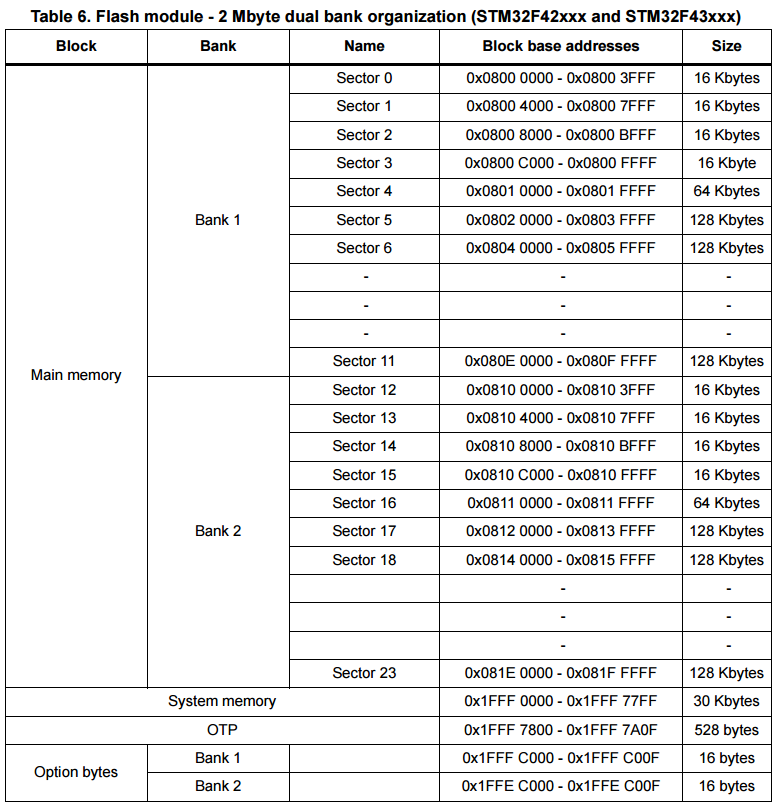

2.3 Flash模組的組成

- Main memory : 由兩個bank組成,每個bank各有4個16Kbytes Sector、1個64Kbytes Sector及7個128Kbytes Sector,一共2048Kbytes(2Mbytes).

- System memory : bootloader code 放置的地方,30Kbytes.

- OTP (One-Time Programmable) : 一次性寫入的空間,共528bytes(512+16),如放軟體version,硬體version,key…等 for user data,可參考(http://forum.eepw.com.cn/thread/120354/1)

- Option byte : 用來設定讀寫保護、電壓level、軟硬體看門狗與Standby or Stop模式下的重置,每個bank各一個,共32(16+16)bytes.

DM00031020-referenceManual

P.77

DM00031020-referenceManual

P.77

STM32F429中的Flash有以下特性:

- 容量2Mbytes,雙bank架構,支援read-while-write(RWW)

- 單次讀取data為128bits

- 單次寫入可以byte, half-word, word以及double word為單位

- 抹除可以sector為單位或是bank以及mass(全部)操作

3 Flash 操作

3.1 Read interface(讀取)

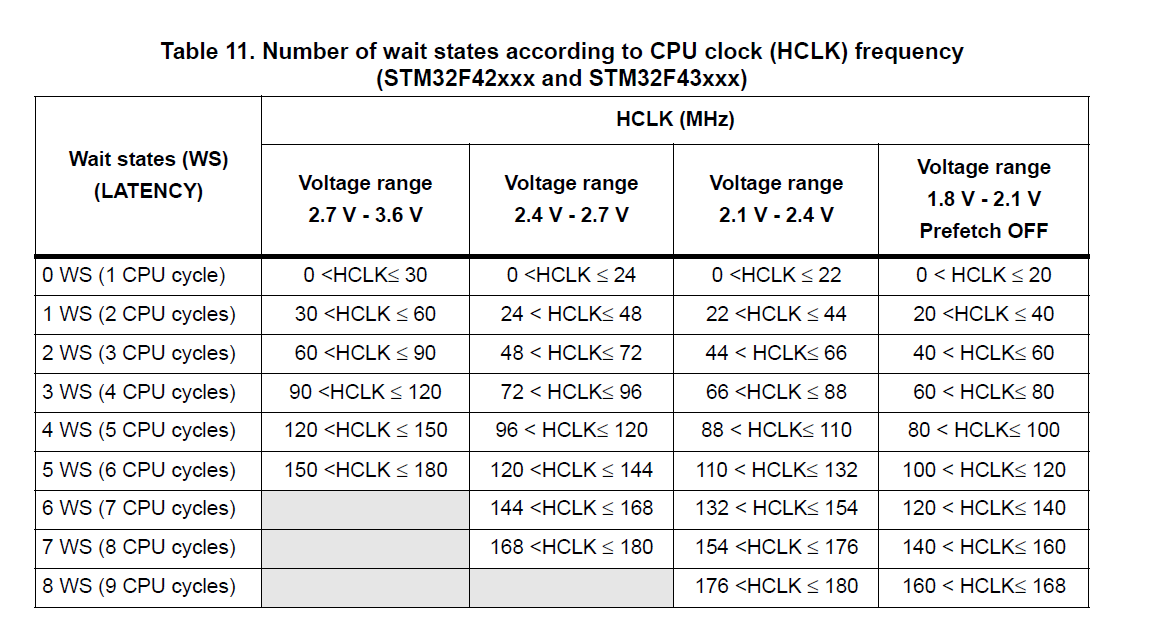

- 為了要正確的從Flash中讀取data,必須在Flash access control register(FLASH_ACR)中,依據CPU clock frequency(HCLK)與device供應的電壓,來設定正確的wait states(LATENCY)值。

- 因為CPU的運行速度遠比Flash快得多,依下表來看,STM32F429的Flash最快access速度為<=30MHZ,如果CPU frequency超過此速度,那就必須增加等待時間。wait states與CPU clock freqency的關係如下表所示 :

DM00031020-referenceManual P.81

DM00031020-referenceManual P.81

- 在Reset之後,CPU clock frequency為16MHz,並且FLASH_ACR中的wait states值被設為0。

- 官方文件建議若要調整wait states值(當加快/減慢CPU frequency時),依據CPU frequency調試存取Flash所需的ws數。

當加快CPU frequency時

- 在FLASH_ACR register中的LATENCY bits設定新的wait states值。

::

000: 0ws(1 CPU cycle) 001: 1ws(2 CPU cycle) 010: 2ws(3 CPU cycle) 011: 3ws(4 CPU cycle) 100: 4ws(5 CPU cycle) 101: 5ws(6 CPU cycle) 110: 6ws(7 CPU cycle) 111: 7ws(8 CPU cycle)

- 透過讀取FLASH_ACR register,確認新的wait states值有被無設定成功。

- 再透過寫入RCC_CFGR(Reset and Clock Control Configuration Register)中的SW(System clock switch) bits來修改 CPU clock source.

::

sw : 00 : HSI (High Speed Internal) 01 : HSE (High Speed External) 10 : PLL (Phase Lock Loop) 11 : not allowed

- 當離開Stop或Standby模式時,或者當HSE Failure時,將由硬體強制轉為HSI。可參考(http://blog.csdn.net/joji_h/article/details/5581340)

- 如果需要,可透過寫入RCC_CFGR register中的HPRE(AHB Prescaler) bits來修改CPU clock prescaler以調整clock freqency.

::

HPRE bits: 0xxx : System clock not divided 1000 : System clock divided by 2 1001 : System clock divided by 4 1010 : System clock divided by 8 … 1111 : System clock divided by 512

- 透過讀取RCC_CFGR register中的SWS(System clock switch status) bits 來確認新的SW(System clock switch) bits有無被設定成功;透過讀取RCC_CFGR register中的來確定新的HPRE(AHB Prescaler) bits有無被設定成功。

當減慢CPU frequency時

- 透過寫入RCC_CFGR(Reset and Clock Control Configuration Register)中的SW(System clock switch) bits來修改 CPU clock source.

- 如果需要,可透過寫入RCC_CFGR register中的HPRE(AHB Prescaler) bits來修改CPU clock prescaler以調整clock freqency.

- 透過讀取讀取RCC_CFGR register中的SWS(System clock switch status) bits 來確認新的SW(System clock switch) bits有無被設定成功;透過讀取RCC_CFGR register中的來確定新的HPRE(AHB Prescaler) bits有無被設定成功。

- 在FLASH_ACR register中的LATENCY bits設定新的wait states值。

- 透過讀取FLASH_ACR register,確認新的wait states值有被無設定成功。

p.s. 加快cpu freqency的step 1~2等於減慢cpu freqency的step4~5;加快cpu freqency的step 3~5等於減慢cpu freqency的step1~3。

3.2 Erase and program operations

操作前需知

- CPU clock frequency必須至少要在1MHZ以上,Flash才能做erase及program的操作,若在操作的途中發生reset,則不保證Flash中內容正確。

- Flash在program/erase操作時,任何欲read Flash的操作會被暫停,需直到program操作完成後,read操作才會被正確的執行。這也代表當program/erase操作正在執行中,code or data fetch(即read)無法執行。

- 在STM32F42xxx和 STM32F43xxx板子上,有兩個bank。故可以支援一bank讀,另一bank寫/抹除。

在做抹除與寫入動作之前,必須先設定Flash control register(FLASH_CR),然而在Reset之後,FLASH_CR是不可寫入的。因此必須透過以下方法解鎖:

- 在Flash key register(FLASH_KEYR)中寫入0x45670123。

- 在Flash key register(FLASH_KEYR)中寫入0xCDEF89AB。

必須連續執行1與2才會解鎖

- 若步驟錯誤一樣會鎖住FLASH_CR,直到reset後才能用以上方式解鎖。

- 若解鎖後要再次鎖住,只要在FLASH_CR中設定LOCK bit即可。

此外,FLASH_CR在FLASH_SR的BSY值為1時是同樣不可寫入的。

3.3 Program/erase parallelism (寫入/抹除並行)

- Parallelism為在操作program或erase時,最大能夠寫幾bit的0。

- PSIZE是在FLASH_CR register中,此值必須在programming/erasing前正確的被寫入。對應表如下表:

DM00031020-referenceManual P.85

- 以下是各種型態單次寫入時所需的大小

- Byte : x8

- Half-word : x16

- Word : x32

- Double-word : x64

3.4 Erase (抹除)

Flash memory erase的操作以sector,bank,Mass(整個flash memory)為單位。

區塊抹除(Sector Erase):

- 檢查Flash status register(FLASH_SR)中BSY(Busy) bit是否為0。(0代表目前沒有其他的Flash操作,1代表有其他Flash操作正在進行中)

- 設定FLASH_CR register中SER(Sector Erase) bit告知啟用區塊抹除,並設定SNB(Sector number) bit告知欲抹除的區塊。

::

SER sector

00000 sector 0

00001 sector 1

...

10111 sector 23

不得超過此範圍。- 設定FLASH_CR register中的STRT(Start) bit。

- 等待FLASH_SR register中的BSY bit清空。(或使用EOP中斷)

bank抹除(Bank Erase):

- 檢查FLASH_SR register中BSY bit是否為0。

- 設定FLASH_CR register中MER(Mass Erase of bank 1)或MER1(Mass Erase of bank 2)bit,告知啟用bank抹除。

- 設定FLASH_CR register中的STRT bit。

- 等待FLASH_SR register中的BSY bit清空。(或使用EOP中斷)

大量抹除(Mass Erase):

- 檢查FLASH_SR register中BSY bit是否為0。

- 設定FLASH_CR register中的MER和MER1 bit。

- 設定FLASH_CR register中的STRT bit。

- 等待FLASH_SR register中的BSY bit清空。(或使用EOP中斷)

注意

- 如果MERx和SER同時被設定,則會執行bank(或mass) erase。

- 如果MERx和SER皆沒被設定,但STRT被設定,此為未定義行為,無法預測後果。

- Mass Erase並不會影響OTP sector或是設定區的sector。

3.5 Program (寫入)

- 基本觀念:

- Flash的每個cell在寫的時候只能1->0,不能從0->1;而erase後,該sector中所有的cell值皆為1。

- 基於上述,當同時需要erase和program的動作時,要先執行erase(0->1),再執行program(1 -> 0)

- 寫入步驟:

- 檢查FLASH_SR register中BSY bit是否為0。

- 設定FLASH_CR中的PG(Programming) bit。

- 在指定的位置(main memory block或OTP area)執行資料寫入的動作。

- 等待FLASH_SR中的BSY bit清空。

- 寫入錯誤:

- 在寫入的過程中,如果出現錯誤,則register FLASH_SR中的Programming errors Flags會被設定。

- PGAERR: 超過128bits的限制

- PGPERR: PSIZE設定錯誤(參考3.3)

- PGSERR: 沒按照標準寫入程序(例: 在寫入Flash memory之前忘記設定PG)

3.6 Read-while-write (RWW)

- 基本觀念:

- 與一般寫入,抹除的方法相同(參考3.4, 3.5)

- Write-while-write 並不允許。因為當有任一bank正在寫入、抹除時,FLASH_SR的BSY bit為1。

- 讀bank1 抹除bank2 當bank1

正在讀取的時候,可以抹除bank2的資料(反之亦然)。操作方法如下

- 檢查FLASH_SR register中BSY bit是否為0。

- 設定FLASH_CR register中MER或MER1 bit,告知啟用bank抹除。

- 設定FLASH_CR register中的STRT bit。

- 等待FLASH_SR register中的BSY bit清空。(或使用EOP中斷)

- 讀bank1 寫bank2 當bank1

正在讀取的時候,可以寫入bank2的資料(反之亦然)。操作方法如下

- 檢查FLASH_SR register中BSY bit是否為0。

- 設定FLASH_CR中的PG(Programming) bit。

- 在指定的位置(main memory block或OTP area)執行資料寫入的動作。

- 等待FLASH_SR中的BSY bit清空。(或使用EOP中斷)

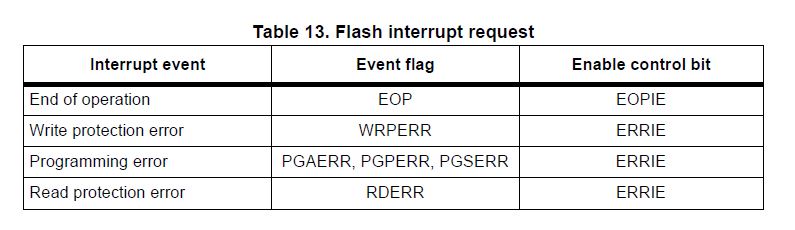

3.7 Interrupt

在erase或program結束時發出中斷

- 設定FLASH_CR register中的end of operation interrupt enable(EOPIE) bit。

- 結束時,FLASH_SR register中的BSY bit為0,而end of operation(EOP) bit為1。

在錯誤時發出中斷

- 在program或erase操作過程中有錯誤發生時,FLASH_SR

register中的某些flag會被設定

- PGAERR, PGPERR, PGSERR (Program error flags)

- WRPERR (Protection error flag)

- RDERR (Read protection error flag)

- 此時,若FLASH_CR register中的error interrupt enable bit(ERRIE)為1,則FLASH_SR register中的operation error bit(OPERR)會在錯誤發生時被設定。

- 在program或erase操作過程中有錯誤發生時,FLASH_SR

register中的某些flag會被設定

DM00031020-referenceManual P.88

DM00031020-referenceManual P.88

3.8 Option bytes

操作步驟

- 在更改option bytes之前,必須先清除FLASH_OPTCR register中的option lock bit(OPTLOCK)

- 但是此bit是受到保護的,要解鎖必須先依序

- 寫入 OPTKEY1 = 0x0819 2A3B 到 Flash option key register (FLASH_OPTKEYR)

- 寫入 OPTKEY2 = 0x4C5D 6E7F 到 Flash option key register (FLASH_OPTKEYR)

- 開始更改時,必須同時更改bank1及bank2的user option

bytes,無法單獨更改。步驟如下

- 檢查FLASH_SR register中BSY bit是否為0

- 將bank2 option bytes的值寫入FLASH_OPTCR1 register

- 將bank1 option bytes的值寫入FLASH_OPTCR register

- 設定FLASH_OPTCR register中的OPTSTRT bit

- 等待FLASH_SR register中的BSY bit清空

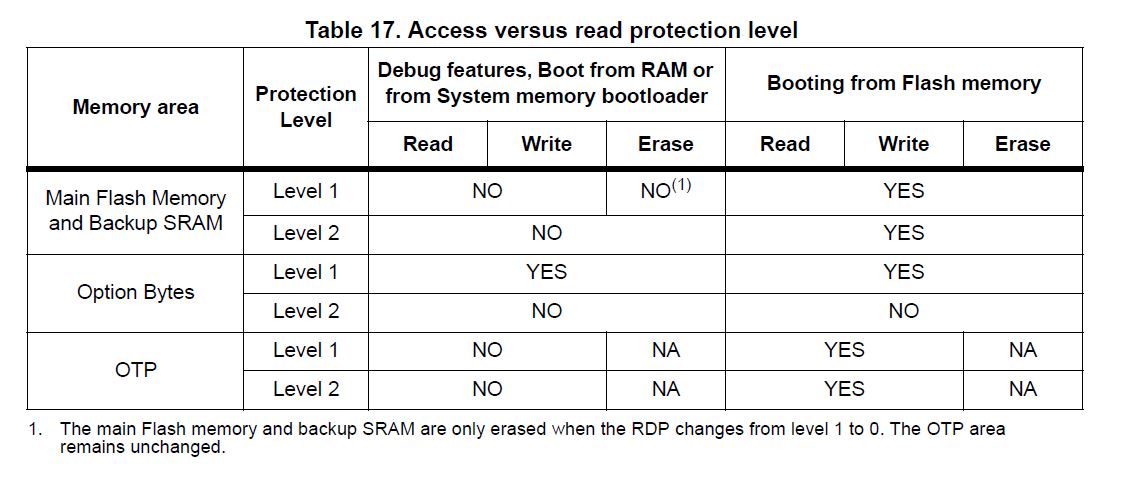

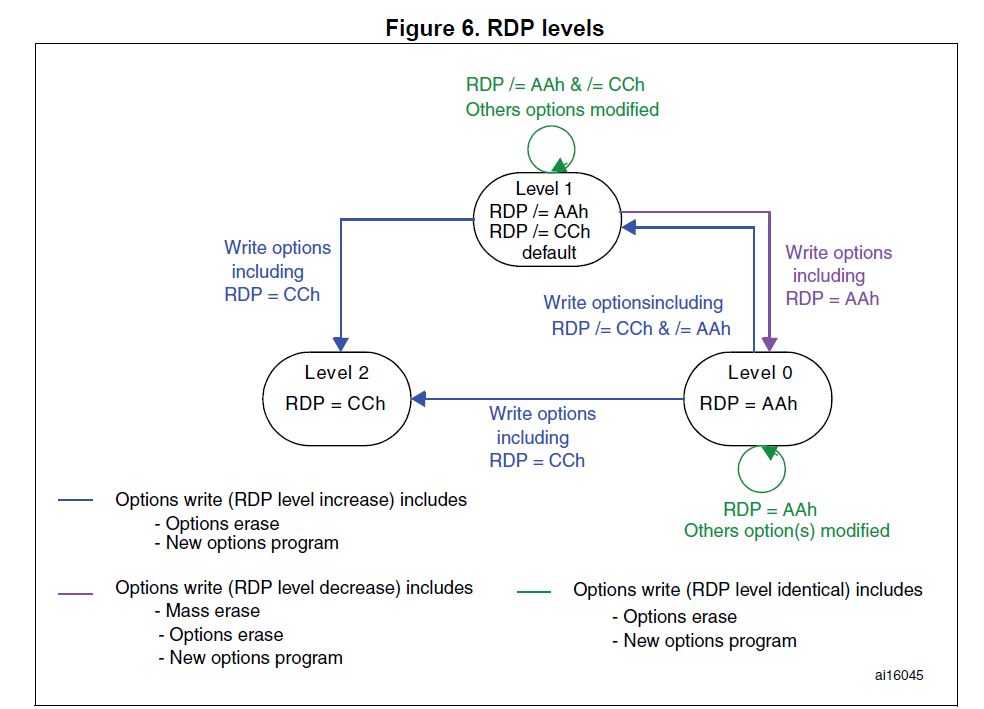

Read Protections(讀取保護)

有三種Read Protections levels:

- Level 0: 無讀取保護

- 將 0xAA 寫入FLASH_OPTCR中的RDP(Read Protection) bit

- 表示Read protection not active。

- Level 1: 開啟讀取保護

- 預設模式,將除了 0xAA 以及 0xCC 以外的值寫入FLASH_OPTCR中的RDP bit

- 由system memory和SRAM啟動且執行的processes無法對Flash memory做存取。

- 由flash memory啟動的程式依然可以存取(讀、寫、抹除)flash memory。

- 若想要降級為level 0,會引發mass erase

- Level 2: 開啟讀取保護,禁用debug/chip

- 將 0xCC 寫入FLASH_OPTCR中的RDP bit

- 所有level 1 的限制皆開啟。

- 不得由 system memory和SRAM執行程式。

- JTAG, SWV (single-wire viewer), ETM, boundary scan皆無法使用。

- User option bytes不能再被更改。

- 由flash memory啟動的程式依然可以存取(讀、寫、抹除)flash memory。

- 一旦設定成level 2以後就無法再更改為level 1 和2。

- Level 0: 無讀取保護

DM00031020-referenceManual P.94

DM00031020-referenceManual P.94

DM00031020-referenceManual

P.94

DM00031020-referenceManual

P.94

- Write Protections(寫入保護)

- 在24個User Sector中(請見5.Flash記憶體架構介紹),Flash memory可以設為保護狀態來避免非預期的寫入操作造成的數據遺失問題。

- 當FLASH_OPTCR或FLASH_OPTCR1 中的nWRPi(non-write protection) bit (0 <= i <= 11)為0時,i所對應的sector就不能夠被寫入或抹除。

- 同樣地,在大量抹除中,只要在抹除範圍內有任何一個Sector是寫入保護的狀態,就不能夠進行抹除。

- 若嘗試在寫入保護的區域中進行寫入/抹除的行為,將會在FLASH_SR中設置WRPERR(Write protection error flag)。

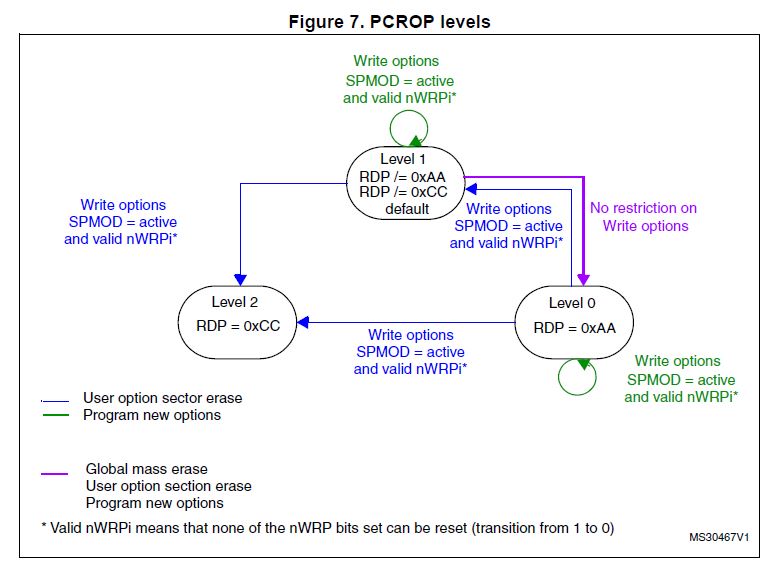

- Proprietary code readout protection (PCROP)

- 使用 proprietary readout protection (PCROP)可以保護 Flash memory user sectors (0到23)不被 D-bus 存取。也就是說,只能夠由I-Bus 抓取指令。

- 可以在FLASH_CR暫存器中的SPRMOD bit 設定PCROP。

- SPRMOD = 0: 關閉PCROP,nWRPi僅控制寫入保護。

- SPRMOD = 1: 開啟PCROP,nWRPi 控制讀寫保護。

- 當PCROP被設置時

- 任何來自D-Bus的讀取會使RDERR(Proprietary readout protection error) flag被設立.

- 任何寫入及抹除的動作會使WRPERR(Write protection error) flag被設立。

DM00031020-referenceManual

P.96

DM00031020-referenceManual

P.96

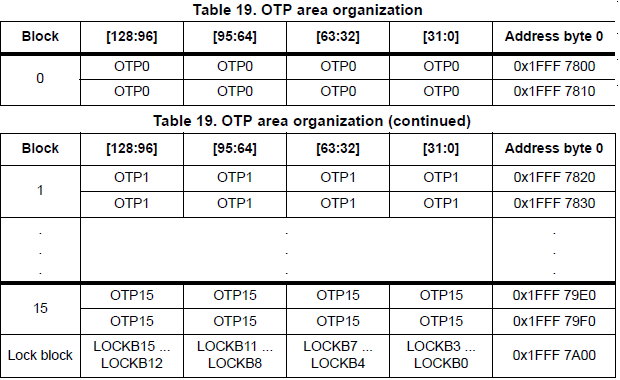

3.9 One-time programmable (OTP)

- 一次性可編程唯讀記憶體(One Time Programmable Read Only Memory,OTPROM)之寫入原理同EPROM,但是為了節省成本,編程寫入之後就不再抹除,因此不設置透明窗(不能被抹除)。

- 總共528 bytes

- OTP bytes(512 bytes)

- OTP lock bytes(16 bytes)

- OTP bytes:16個block,每個block有32bytes(總共512 bytes)–for user data

- OTP lock bytes:有16 bytes LOCKBi (0 ≤ i ≤ 15)分別控制相對應的16個block–for locking the correspaonding OTP

- 在OTP lock byte 為 0x00 的時候,OTP 才可以被寫入資料(原本為0xFF);而OTP block byte只能為0x00或是0xFF,否則OTP可能會讀不到正確的值

DM00031020-referenceManual P.97

DM00031020-referenceManual P.97

4 Flash interface registers

- read/write (rw) :Software can read and write to these bits.

- read-only (r) :Software can only read these bits.

- write-only (w) :Software can only write to this bit. Reading the bit returns the reset value.

- read/clear (rc_w1) :Software can read as well as clear this bit by writing 1. Writing ‘0’ has no effect on the bit value.

- read/clear (rc_w0) :Software can read as well as clear this bit by writing 0. Writing ‘1’ has no effect on the bit value.

- read/set (rs) :Software can read as well as set this bit. Writing ‘0’ has no effect on the bit value.

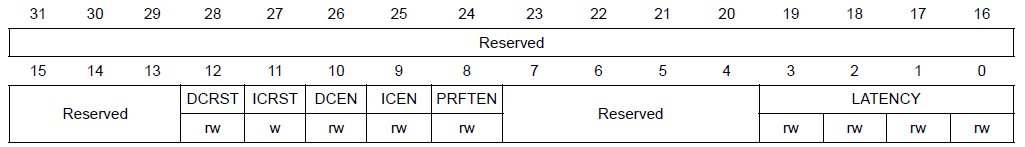

4.1 Flash access control register (FLASH_ACR)

- 用來控制Flash memory的存取速度(根據CPU的頻率)、開啟關閉加速功能

- Address offset: 0x00

- Reset value: 0x0000 0000

- Bits 31:13 保留位置,必須保持淨空。

- Bit 12 DCRST : Data cache reset. 0: not reset; 1: reset. (當D cache未啟用時才可寫入)

- Bit 11 ICRST : Instruction cache reset. 0: not reset ; 1: reset. (當I cache未啟用時才可寫入)

- Bit 10 DCEN : Data cache enable. 0: disabled; 1: enabled.

- Bit 9 ICEN : Instruction cache enable. 0: disabled; 1: enabled.

- Bit 8 PRFTEN : Prefetch enable. 0: disabled; 1: enabled;

- Bits 7:4 保留位置,必須保持淨空。

- Bits 3:0 LATENCY: Latency

- CPU時脈/Flash memory存取時間

- 0000: Zero wait state

- 0001: One wait state

- 0010: Two wait states

- …

- 1110: Fourteen wait states

- 1111: Fifteen wait states

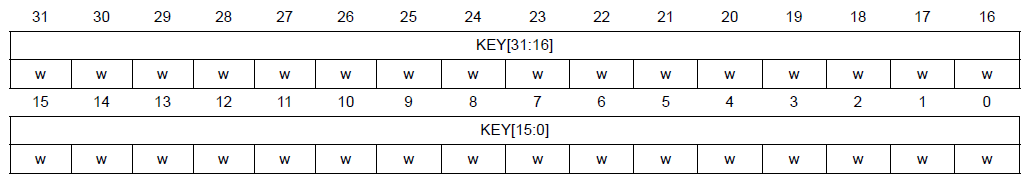

4.2 Flash key register (FLASH_KEYR)

- 用來允許存取Flash control register、program和清除operations

- Bits 31:0 FKEYR: FPEC key

- The following values must be programmed consecutively to unlock the

FLASH_CR register and allow programming/erasing it:

- KEY1 = 0x45670123

- KEY2 = 0xCDEF89AB

- The following values must be programmed consecutively to unlock the

FLASH_CR register and allow programming/erasing it:

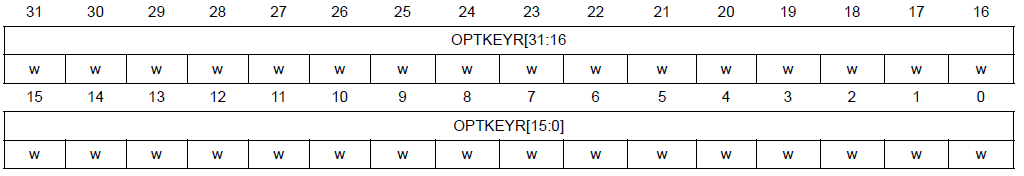

4.3 Flash option key register (FLASH_OPTKEYR)

- 允許在user configuration sector裡執行程式和清除operations

- Address offset: 0x08

- Reset value: 0x0000 0000

- Bits 31:0 OPTKEYR: Option byte key

- The following values must be programmed consecutively to unlock the

FLASH_OPTCR register and allow programming it:

- OPTKEY1 = 0x08192A3B

- OPTKEY2 = 0x4C5D6E7F

- The following values must be programmed consecutively to unlock the

FLASH_OPTCR register and allow programming it:

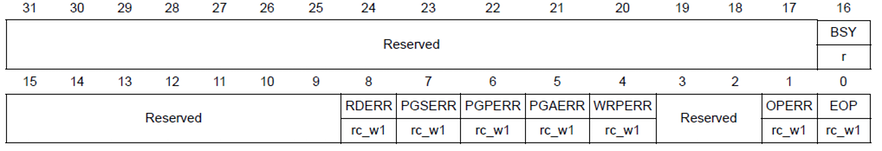

4.4 Flash status register (FLASH_SR)

- 執行中的程式和erase operation的資訊

- Address offset: 0x0C

- Reset value: 0x0000 0000

- Bits 31:17 Reserved, must be kept cleared.

- Bit 16 BSY : Busy. 0: 無其他記憶體操作; 1: 其他記憶體操作進行中。(若無任何操作時會自動清除)

- Bits 15:9 Reserved, must be kept cleared.

- Bit 8 RDERR: Proprietary readout protection (PCROP) error

- 當read access經由D-bus讀取位址(屬於proprietary readout protected Flash)時,由硬體設值,寫入1時清空

- Bit 7 PGSERR : Programming sequence error. 當程式出現錯誤時會設值。若寫入1則清空。

- Bit 6 PGPERR : Programming parallelism error. 當程式寫入大小與型態不符(對照PSIZE)時會設值。若寫入1則清空。

- Bit 5 PGAERR : Programming alignment error. 當資料寫入時無法塞入128-bit的Flash memory row會設值。若寫入1則清空。

- Bit 4 WRPERR : Write protection error. 當嘗試寫入/抹除一個寫入保護的Flash memory區域時會設值。若寫入1則清空。

- Bits 3:2 Reserved, must be kept cleared.

- Bit 1 OPERR : Operation error. 當任何的Flash操作失效時設值,但這個bit只會在ERRIE(Error Interrupts)啟用時生效。

- Bit 0 EOP : End of Operation. 當一或多個Flash操作成功完成時設值,這個bit只會在EOPIE(End of Operation Interrupts)啟用時生效。若寫入1則清空。

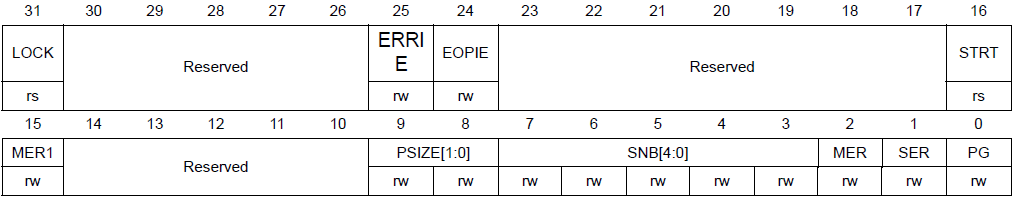

4.5 Flash control register(FLASH_CR)

- used to configure and start Flash memory operations.

- Address offset: 0x10

- Reset value: 0x8000 0000

- Bit 31 LOCK : Lock. 只能寫為1,當值為1時,FLASH_CR將鎖住不可更改,唯有偵測到解鎖序列才會清除。

- Bits 30:26 保留位置,必須保持淨空。

- Bit 25 ERRIE: Error interrupt enable. 0: Disabled; 1: Enabled.

- Bit 24 EOPIE: End of operation interrupt enable. 0: Disabled; 1: Enabled.

- Bits 23:17 保留位置,必須保持淨空。

- Bit 16 STRT: Start. 只能由軟體設置,且在BSY bit清空時會一併清空。

- Bits 15:10 保留位置,必須保持淨空。

- Bits 9:8 PSIZE: Program size.

- These bits select the program parallelism.

- 00 program x8

- 01 program x16

- 10 program x32

- 11 program x64

- Bits 7:3 SNB: Sector number.

- These bits select the sector to erase.

- 0000: sector 0

- 0001: sector 1

- …

- 01011: sector 11

- 01100: not allowed

- 01101: not allowed

- 01110: not allowed

- 01111: not allowed

- 10000: section 12

- 10001: section 13

- …

- 11011 sector 23

- 11100: not allowed

- 11101: not allowed

- 11110: not allowed

- 11111: not allowed

- Bit 2 MER: Mass Erase.

- Bit 1 SER: Sector Erase.

- Bit 0 PG: Programming.

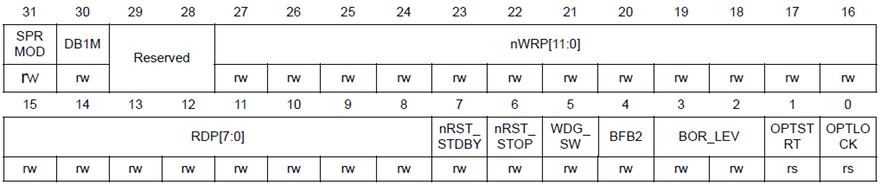

4.6 Flash option control register (FLASH_OPTCR)

- modify the user option bytes.

- Address offset: 0x14

- Reset value: 0x0FFF AAED.

- Bits 31 SPRMOD: Selection of protection mode for nWPRi bits

- 0: PCROP disabled. nWPRi bits used for Write protection on sector i.

- 1: PCROP enabled. nWPRi bits used for PCROP protection on sector i

- Bits 30 DB1M: Dual-bank on 1 Mbyte Flash memory

devices(我們使用的板子flash是2Mbytes)

- 0: 1 Mbyte single bank Flash memory (contiguous addresses in bank1)

- 1: 1 Mbyte dual bank Flash memory.

- Bits 29:28 保留位置,必須保持淨空。

- Bits 27:16 nWRP: Not write protect. 0: write protection active; 1: write protection not active.

- Bits 15:8 RDP: Read protect. 0xAA : Level 0, read protection not active; 0xCC : Level 2, chip read protection active; Others : Level 1, read - protection of memories active.

- Bits 7:5 USER: User option bytes

- Bit 4 保留位置,必須保持淨空。

- Bits 3:2 BOR_Level: BOR reset level.

- 00 : BOR level 3, 電壓 2.70~3.60V

- 01 : BOR level 2, 電壓 2.40~2.70V

- 10 : BOR level 1, 電壓 2.10~2.40V

- 11 : BOR off, 電壓 1.80~2.10V

- Bit 1 OPTSTRT: Option start.

- Bit 0 OPTLOCK: Option lock.

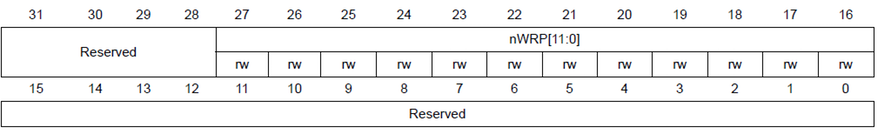

4.7 Flash option control register (FLASH_OPTCR1)

- available only on STM32F42xxx and STM32F43xxx.

- used to modify the user option bytes for bank 2

- Address offset: 0x18

- Reset value: 0x0FFF 0000.

- Bits 31:28 Reserved, must be kept cleared.

- Bits 27:16 nWRP: Not write protect. 0: write protection active; 1: write protection not active.

- Bits 15:0 Reserved, must be kept cleared.

5.Example

5.1 下載

- firmware: STM32F429I-Discovery_FW_V1.0.1 http://www.st.com/web/en/catalog/tools/PF259429

- git clone https://github.com/cdfq152313/stm32F429-flash.git

- 放在同一目錄下

5.2 操作流程 (節錄)

- 設定正確的Latency。具體流程參閱3.1

::

SetSysClockTo84();

======= 在 SetSysClockTo84() 函式中 ======

FLASH_SetLatency(FLASH_Latency_2);

RCC_PLLConfig(RCC_PLLSource_HSE, 6, 252, 4, 7);

- 解鎖flash,具體流程參閱3.2

::

FLASH_Unlock();- 清除所有flag,參閱4.4

::

FLASH_ClearFlag(FLASH_FLAG_EOP | FLASH_FLAG_OPERR | FLASH_FLAG_WRPERR |

FLASH_FLAG_PGAERR | FLASH_FLAG_PGPERR|FLASH_FLAG_PGSERR); - 清除sector 12和13,FLASH_EraseSector若失敗會回傳非FLASH_COMPLETE之值。

- 具體流程參閱3.4

::

erase_data(GetSector(ADDR_FLASH_SECTOR_12), GetSector(ADDR_FLASH_SECTOR_13) );

====================在 erase_data 函式中 =====================

if (FLASH_EraseSector(uwSectorCounter, VoltageRange_3) != FLASH_COMPLETE)

...- 將資料寫入的sector 12,FLASH_ProgramWord(uwAddress, DATA_32)若失敗會回傳非FLASH_COMPLETE之值。

- 具體流程參閱3.5

::

program_data(ADDR_FLASH_SECTOR_12, ADDR_FLASH_SECTOR_13);

====================在 program_data 函式中 =====================

FLASH_ProgramWord(uwAddress, DATA_32) == FLASH_COMPLETE- 使用寫入保護設定第13個sector,參閱3.8

::

FLASH_OB_Unlock();

FLASH_OB_WRP1Config(OB_WRP_Sector_13, ENABLE);

if (FLASH_OB_Launch() != FLASH_COMPLETE)

USART1_puts("Write protection error...\r\n");

FLASH_OB_Lock();- 保護後,試圖寫入sector 13 會失敗。

::

program_data(ADDR_FLASH_SECTOR_13, ADDR_FLASH_SECTOR_14);- 鎖起FLASH

::

FLASH_Lock(); 5.3 相關API

- 請參閱 firmware

- (firmware)/Libraries/STM32F4xx_StdPeriph_Driver/src/stm32f4xx_flash.c

- (firmware)/Libraries/STM32F4xx_StdPeriph_Driver/src/stm32f4xx_flash.h

5.4 程式結果 (由usart傳出)

::

flash demo start

Flash unlock

Erase sector 12 13

Sector 12 (first 80 bytes)

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

Sector 13 (first 80 bytes)

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

Program 0x32F429DC to sector 12

Sector 12 (first 80 bytes)

32F429DC 32F429DC 32F429DC 32F429DC

32F429DC 32F429DC 32F429DC 32F429DC

32F429DC 32F429DC 32F429DC 32F429DC

32F429DC 32F429DC 32F429DC 32F429DC

32F429DC 32F429DC 32F429DC 32F429DC

Enable write protection to sector 13

Attempt to program 0x32F429DC to sector 13

sector 13 (first 80 bytes)

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF

Flash lock6.reference

- https://github.com/cdfq152313/stm32F429-flash

- http://wiki.csie.ncku.edu.tw/embedded/learn-stm32-part-1.pdf

- http://wiki.csie.ncku.edu.tw/embedded/learn-stm32-part-6.pdf

- http://www.triplespark.net/elec/pdev/arm/stm32.html

- http://www.codeproject.com/Articles/14983/Remote-Debugging-using-GDB

- http://cms.mcuapps.com/products/stm32f4-discovery/README.html

- http://cms.mcuapps.com/techinfo/toolchains/openocd/

- http://www.st.com/internet/mcu/product/252140.jsp

- http://zh.wikipedia.org/wiki/%E9%97%AA%E5%AD%98

- 快閃記憶體(wiki)

- http://www.eetasia.com/ART_8800627935_480200_NT_1866240e.HTM

- http://www.xuan.idv.tw/wordpress/?p=821

- Nand Flash 基本介紹

- Nand Flash BBT Support in Linux

- http://www.ptt.cc/bbs/NTU-EM93/M.1253794167.A.8F8.html

- [轉載]Nand flash結構以及讀寫經典分析